● 학습목표 : 디버깅 장비, AVR 디버거 장비, TRACE32 장비의 이해

└ 위 장비를 이해하고 활용

1. 디버거 장비의 이해

1) 디버깅 : 프로그램이나 하드웨어 장치의 문제점을 찾고 해결하는 것.

-. 임베디드 시스템은 호스트 컴퓨터에 SW제작 툴이 있고 타겟 보드에 디버깅 할 프로그램이 있다보니 둘을 연결해줄 디버거 장비가 필요해진다. (디버거 장비는 타겟보드 CPU에 따라 결정됨)

2) 소스레벨 디버깅 : 프로그램 소스코드를 확인하면서 디버깅하는것을 말함. 즉, 프로그램 소스를 확인하면서 프로그램 진행을 멈추게 할 수 있고, 확인하고 싶은 변수나 메모리, 어셈블리어의 값, CPU의 상태까지도 확인이 가능한 디버깅.

Ex) 비쥬얼 스튜디오에서의 소스레벨 디버깅 하기

① 커서를 원하는 위치에 두고 F9를 눌러 중단점을 설정.

② F5를 눌러 디버깅 시작

③ F10을 눌러 한 라인씩 디버깅

④ 소스레벨 단위에서 라인별로 에러가 발생하는 여부를 확인

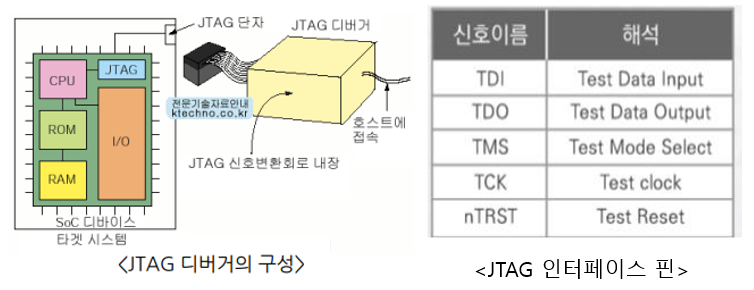

3) JTAG의 개요

-. 디버거 : 에뮬레이터라는 용어와 혼용해서 많이 사용하는데, 왜냐하면 JTAG이라는 디버깅 방식이 개발되기 전에는 에뮬레이터라는 방식으로 제작됨.

-. 에뮬레이터 : CPU나 메모리의 동작을 흉내내어주는 디버깅에 사용하는 장비나 소프트웨어를 말함.

└ 고가이며 CPU 동작 주파수가 100Mhz이상 되면 제조가 어려움 등 문제가 많아지며 JTAG이 개발됨.

-. JTAG(Joint Test Action Group) 방식 : 외부로 나온 핀을 직접 접촉하지 않고 테스트 목적의 셀을 칩 내부에 장착하여 전용 Data IN으로 특정값을 입력하여 Data OUT으로 특정 값이 나오는지를 확인하는 방식. 이러한 방식을 통해 PCB보드 검증뿐만 아니라 디버거를 만드는 방식에서 활용

-. JTAG 디버거 : JTAG단자라고 하는 몇개의 신호만 연결하면 디버깅이 가능한 장비.

└ JTAG인터페이스 핀 설명 (하기 5개 外 nRESET, nSRST, Vtref, DBGRQ, DBGACK 등 신호가 추가되기도함)

TDI : 테스트할 데이터 입력

TDO : 결과 데이터를 출력

TMS : 디버깅을 위한 컨트롤러의 모드를 제어하는 신호

TCK : 컨트롤러를 위한 클럭 신호

nTRST : 모드를 위한 리셋 신호

-. IEEE 1149.1 디바이스의 구조 : Internal Core Logic과 이를 테스트하고 검증할 JATG블록을 추가한 구조.

└ Internal Core Logic : 칩 내부 본래의 기능

└ JATG블록은 Bypass, Instrction, Identification, TAP Controller로 구성되며 TDI와 TDO로 데이터를 주고 받음.

└ TMS, TCK, TRST 신호는 TAP Controller를 제어하는데 사용됨. (TAP의 상태에 따라 TDI가 명령일수도, 데이터일 수도 있으며, TDO도 어드레이스일수도, 데이터일수도 있음)

└ 즉, JTAG을 이용한다는 것은 TAP컨트롤러를 제어하여 필요한 명령이나 데이터를 읽고 쓰는 방식이다.

-. JTAG Pin 배치 : CPU코어의 종류나 버전에 따라 다양한 핀 배치를 가진다.

Ex) AVR의 JTAG핀 맵

-. JTAG Pin의 기능

└ TMS(Test Mode Select) : 디버깅 상태에서 Scan Chain을 결정하고 Bypass 같은 디버깅모드를 선택하는데 사용

└ TCK(Test ClocK) : JTAG을 구동하는 clock으로 보통의 경우 10Mhz를 사용

└ nTRST(Test Reset) : JTAG의 Tap 컨트롤러를 리셋시키는 역할

└ VTref(Test Voltage reference) : JTAG 인터페이스의 입/출력 전압 레벨을 설정하는 단자. 이는 에뮬레이터에 전원공급용으로 사용되지 않아 JTAG Logic이 들어있는 프로세서의 전압은 따로 공급되어야 함.

└ nSRTS(=nRESET) : Target CPU를 Reset하거나 Reset을 검출하기 위해 사용 (장비에서 특수명령어로 이용가능)

└ DBGRQ : 외부 trigger signal을 사용하여 프로그램 실행을 멈출 수 있도록 해줌

└ DBGACK : 정확한 프로그램 실행시간을 측정해주며 프로그램 실행을 정지할 때 다른 디바이스를 정확하게 Triggering할 수 있도록 해준다.

└ RTCK(Return Test Clock) : Target의 JTAG 포트(또는 프로세서)로부터 JTAG 디버거 쪽으로 입력되는 신호. 프로세서의 내부 Clock에 동기시켜야 하는 코어인 경우 반드시 연결해 주어야 함.

2. AVR 디버거 장비의 이해

1) ISP 장비 : CPU 내부의 플래시 메모리, EEPROM 등을 지우거나 프로그래밍하는 기능만 가능한 장비

2) JTAG 장비 : 플래시 메모리를 프로그래밍하는 기능과 더불어 소스레벨 디버깅이 가능한 장비

3) ISP(In System Programming) 방식 : AVR의 플래쉬 메모리에 직렬 통신으로 실행 프로그램을 다운로드하는 방식으로 기존 외부 RAM, 롬 에뮬레이터 및 롬 라이터를 사용하는 방법에 비해 매우 편리한 방법 (ISP 기능을 사용하기 위해서는 ISP 프로그래머가 필요)

4) ISP프로그래머의 연결 : USB방식은 PC에 VCP 드라이버가 설치되어야 사용 가능. ∵ 인터페이스는 USB포트 이지만 인터페이스는 가상의 직렬포트로 설정해서 사용하기 때문

5) ISP방식의 하드웨어 인터페이스 : AVR의 ISP는 6핀방식고 10핀방식이 있음(그라운드신호 추가에 따른 차이)

6) SPI(Serial Peripheral Interface) : 마스터와 슬레이브 개념을 이용한 통신

-. MISO : Master Input Slave Output

-. MOSI : Master Output Slave Input

-. SCK : Serial Clock

-. SS(Slave Select) : 여러개의 Slave가 존재할때 선택하는 신호

3. TRACE32 장비의 이해

참고) TRACE32 : 거의 모든 CPU코어를 지원하지만 CPU코어 별로 별도의 라이센스를 사야함. JTAG 장비 중 가장 비싼 편.

참고) OpenOCD : JTAG 장비중 비교적 저렴한 장비.

1) TRACE32장비의 설치

-. PowerView 설치 : 호스트 PC에 PowerView라는 프로그램을 설치한 후 USB를 통해 연결하여 사용. (사용할 CPU코어의 종류를 확실하게 지정해서 설치해야 함)

-. TRACE32 장비는 3개의 LED가 있는데 Power LED는 장비에 전원이 공급여부, Select LED는 장비와 PC가 연결되었는지 여부, EMULATE LED는 타겟 보드와 장비가 연결되어 디버깅 동작을 수행하는지 여부를 나타 낸다.

-. 라이센스 케이블 : 디버깅 할 수 있는 CPU코어의 종류에 대한 정보가 들어있음.

'Knowledge Dump' 카테고리의 다른 글

| ISTQB CTFL 요점정리 1) 사전학습(용어 해설) (0) | 2022.06.29 |

|---|---|

| ISTQB CTFL 자격증 취득 0) 시험/합격 후기 (0) | 2022.06.27 |

| 데이터시트 분석하기 기초 (0) | 2021.08.18 |

| 회로도 분석하기 기초 (0) | 2021.08.18 |

| 펌웨어란 무엇인가 (0) | 2021.08.12 |